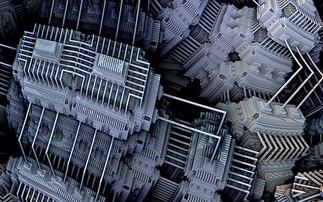

Chipmaker talks up innovative features of next-generation processor designs

AMD is tweaking the design of its upcoming Carrizo family of accelerated processing units (APUs) to make them more compact and efficient. This will boost performance, save power and deliver double-...

To continue reading this article...

Join Computing

- Unlimited access to real-time news, analysis and opinion from the technology industry

- Receive important and breaking news in our daily newsletter

- Be the first to hear about our events and awards programmes

- Join live member only interviews with IT leaders at the ‘IT Lounge’; your chance to ask your burning tech questions and have them answered

- Access to the Computing Delta hub providing market intelligence and research

- Receive our members-only newsletter with exclusive opinion pieces from senior IT Leaders