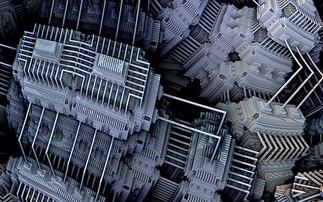

Forthcoming chip with four CPU and one GPU cores will also be power-efficient

AMD's Fusion project aims to combine CPU and GPU elements on a single chip AMD is to disclose details of its first Fusion processor today at the International Solid State Circuits Conference (ISS...

To continue reading this article...

Join Computing

- Unlimited access to real-time news, analysis and opinion from the technology industry

- Receive important and breaking news in our daily newsletter

- Be the first to hear about our events and awards programmes

- Join live member only interviews with IT leaders at the ‘IT Lounge’; your chance to ask your burning tech questions and have them answered

- Access to the Computing Delta hub providing market intelligence and research

- Receive our members-only newsletter with exclusive opinion pieces from senior IT Leaders